| 5. |

I, G |

Deposito programma.

I registri deposito dati, tutti o in parte secondo necessità, possono essere raddoppiati

(splittati), riducendone la capacità del singolo registro a 12 Crt .

L’effetto si ottiene accompagnando il tasto indirizzo con il tasto split (/).

La seconda parte del registro, definita splittata, è indirizzata con lettera minuscola, b, c,

d, e, f.

La lunghezza di un dato, introdotto da tastiera o risultante dal calcolo, non può superare i

23 Crt nel registro intero o 11 Crt nel registro splittato.

I registri sono specializzati per:

- Tipo di informazione. Dati o programma.

- Tipo di utilizzo. Calcolo e/o deposito oppure solo deposito.

- Dimensione. Intero (24 Crt) o Splittato (12 Crt).

Se l’istruzione non contiene l’indirizzo del registro, bit TA – TC = 0, viene selezionato

implicitamente il registro M.

Il registro A per la sua funzione in calcolo viene anche detto “accumulatore”.

I registri M, A e R sono richiamati e modificati durante il calcolo in modo implicito.

I registri deposito dati B, C, D, E, F, sono sempre caricati da istruzioni di trasferimento

che hanno come indirizzo implicito M o A.

Le istruzioni eseguono il trasferimento, dopo l’allineamento di M ed A, sul 1° Crt se

registro intero o sul 13° Crt se splittato.

I dati nei registri deposito saranno sempre allineati.

I registri F, E, D, splittati possono contenere promiscuamente dati e programma.

I registri G e I non sono selezionabili da programma, essi sono anche indicati come

registro programma 1 e 2 e possono contenere solo istruzioni.

Il programma ha disponibili massimo 5 * 24 = 120 istruzioni.

16In introduzione programma, da cartolina o tastiera, i registri di programma sono ad

accesso sequenziale e in sequenza fissa a partire da G (1), I (2), F, E , D e sempre a

partire dal 1° Crt.

Se il programma è avviato mediante tasto di salto, la prima istruzione eseguita è quella

seguente il riferimento corrispondente.

Se il programma viene avviato per la prima volta con il tasto S, la prima istruzione

eseguita è quella contenuta nella posizione del primo carattere del registro G.

Il registro contenente l’istruzione in esecuzione, cambia a fine esecuzione dell’istruzione

nel suo 24° Crt o in seguito dell’esecuzione di una istruzione di salto con riferimento

posto in altro registro.

Carattere del registro

| I registri A, M, R , B, C possono contenere solo dati.

|

| I registri D, E, F possono contenere sia dati che istruzioni. è la logica del programma a definire il tipo di informazione nel registro.

|

| I registri G (Programma 1), I (Programma 2) possono contenere solo istruzioni.

Il numero indirizzabile di registri dati oggetto di istruzioni, può variare da :

{\

|

| Minimo |

5 |

Registri M, A, R, C ,D |

Interi.

|

| Massimo |

13 |

Registri M, A, R |

Interi.

|

|

Registri B, C, D, E, F, b, c, d, e, f |

Splittati.

|

Dato

Il Crt è diviso logicamente in due parti :

TA – TD

TE – TH

Bit di servizio:

TA

Bit riservato per funzioni sia di sistema che calcolo numerico.

TB

Cifra valida.

TC

Dato negativo.

TD

Cifra accompagnata da virgola.

Bit specificanti la cifra . Peso del bit TE 2 0 , TF 2 1 , TG 2 2 , TH 2 3 .

I bit TA e TD o sono assenti o compaiono nel registro su un solo Crt.

Il bit TB compare su tutte le cifre decimali o intere valide.

Il bit TC compare su tutte le cifre se il numero è negativo.

Il bit TD è inserito nella cifra delle unità (10 0 ).

17Al reset, i registri M, A e R sono inizializzati con i bit di servizio TA – TD, del 24° Crt = 1.

Si ha il duplice effetto di inizializzare i registri con:

• Digit –0.

• TA, bit che individua il punto di inserimento dei dati da tastiera o cartolina.

Il trasferimento di un registro deposito in A comporta la scrittura di -0 sul 24° Crt.

I dati in B, C, D, E, F , b, c, d, e, f, registri deposito sono sempre allineati, cifra meno

significativa nella 1 a posizione dopo il gap. Se registro splittato cifra meno significativa

nella 13 a posizione dopo il gap.

Tutte le altre cifre seguono senza intervalli.

Essendo i primi 4 bit del Crt di servizio, un Crt contiene una cifra (digit) .

Il dato significativo può avere un numero di cifre variabile, sia totale che decimali.

Il limite massimo è di 23 Crt se registro intero, 11 Crt se registro splittato.

Il numero di cifre decimali può alla fine del calcolo essere massimo di 22.

Esempio

9,1234567890123456789012 totale 23 cifre.

Il risultato formattato nel registro A, avrà sempre un numero di cifre decimali pari a

quanto impostato sulla rotella decimali. Massimo 15.

I dati nei registri, M A o R , in conseguenza delle istruzioni di calcolo scorrono nei registri

e alla fine non sono più allineate ai riferimenti iniziali.

La posizione finale dipende dall’istruzione e dal valore dei dati.

La natura sequenziale dell’algoritmo di calcolo e del flusso dei dati non richiede di

conoscere il peso della cifra. Si deve controllare solo la sua posizione relativa rispetto la

virgola.

L’informazione di dato valido, necessaria per iniziare e finire il calcolo, è data da flip flop

mantenuti set dalla presenza di bit TB e reset dalla sua assenza.

Si ottiene un effetto “integratore”, forma d’onda a 1 con TB=1, a partire dalla cifra meno

significativa, a 0 con TB=0 nel Crt che segue la cifra più significativa.

I flip flop che implementano la funzione dato valido sono tre:

PM

PA

TP

Registro M.

Registro A.

Registro dati selezionato dal codice istruzione.

Istruzione

Le istruzioni, tranne quelle di salto e relativi riferimenti, rispettano tutte lo stesso tipo di

codifica.

I primi quattro bit TA – TD, codificano la selezione del registro.

Essendo esclusi dalla selezione i registri I e G dedicati a solo programma, i restanti 8

registri sono selezionati tramite i primi 3 bit TA – TC.

Il quarto bit TD se posto a 1, indica la condizione di split, registro diviso in due.

Nel foglio di programmazione la lettera specificante il registro, indica se:

• Maiuscola

Registro intero o 1 a parte di registro splittato.

• Minuscola

2 a parte di registro splittato.

Tabella codifica indirizzi di selezione registro. Bit TA – TD.

Registro

TA TB TC TD

0

1

0

1

0

1

0

1

0 0

0

1

1

0

0

1

1

0 0

0

0

0

1

1

1

1

0 0

0

0

0

0

0

0

0

1

c HEX

0

1

2

3

4

5

6

7

8

9 0 0 0 1

R

d

A

b

f

e A

B

C

D

E

F 0

1

0

1

0

1 1

1

0

0

1

1 0

0

1

1

1

1 1

1

1

1

1

1

M

C

R

D

A

B

F

E

/

I secondi quattro bit TE – TF, codificano la selezione della istruzione.

Il codice A esadecimale non è utilizzato.

Tabella codifica istruzioni. Bit TE – TH.

19Istruzione Tasto

Start

Registro in A

M in registro

Scambio Registro con A

Somma

Sottrazione

Moltiplica

Divisione

Stampa S

↓

↑

↕

+

-

Azzera Registro

Codice Libero

Radice Quadrata

Salto V

Salto W

Salto Y

Salto Z

TE TF TG TH

0

1

0

1

0

1

0

1

0 0

0

1

1

0

0

1

1

0 0

0

0

0

1

1

1

1

0 0

0

0

0

0

0

0

0

1

0

1

2

3

4

5

6

7

8

9 0 0 0 1

NU

√

V

W

Y

Z A

B

C

D

E

F 0

1

0

1

0

1 1

1

0

0

1

1 0

0

1

1

1

1 1

1

1

1

1

1

x

◊

Salto

Le istruzioni di salto utilizzano bit riservati nelle altre istruzioni alla selezione del registro :

1. TA e TB

2. TC

3. TD

Estendono i codici riservati ai salti.

Distingue tra salto(0) e riferimento (1).

Distingue tra salto incondizionato (0) o condizionato (1).

I codici operativi delle istruzioni di salto sono 4, ad essi sono riservati i codici CX, DX, EX

ed FX a cui si fanno corrispondere i tasti V, W, Y e Z.

Il decodificatore in hardware dei salti è ZM.

La condizione da verificare nel salto condizionato, è data dal dato del registro A, esso

deve essere positivo, precisamente >0, perché il salto venga eseguito.

I codici di salto utili diventano 16, dato che ogni codice operativo, utilizza i bit TA e TB del

Crt, per distinguerne 4 diversi.

Riassumendo si hanno 16 salti incondizionati, 16 condizionati e 16 riferimenti.

Cartolina

La cartolina è il supporto magnetico utilizzato per memorizzare permanentemente i

programmi della P101.

La cartolina ha una capacità massima di 5 registri (G, I, F, E, D), 120 Crt di coppie

indirizzo – istruzione.

La lettura della cartolina richiede:

• Macchina in stato SA.

• Introduzione di cartolina nel meccanismo di trascinamento.

La scrittura della cartolina richiede:

• Macchina in stato SA.

• Abbassamento del pulsante bistabile AP.

• Introduzione di cartolina nel meccanismo di trascinamento.

L’abbassamento di AP ed AZ, determina la registrazione / lettura di una cartolina corta, 2

registri (E, D), 48 istruzioni.

La presenza della cartolina sotto la testina è segnalata da un μswitch (AO).

Il flip flop SO che memorizza lo stato di AO, indica il periodo utile di registrazione/lettura

del supporto.

Il flip flop NM, mantiene la sua funzione di pulizia dei registri, la stessa utilizzata per

introduzione dati da tastiera, prima di essere settato dal primo ciclo di trasferimento Crt.

NM riposiziona il TA di R in TR, cancellando quello precedente. In caso di lettura cartolina,

NM tramite XY, blocca la richiusura sulla LDR dei registri G, I, F, E, D azzerandoli.

Formato carattere cartolina

Diagramma Formato Crt cartolina.

La cartolina è un supporto di memoria il cui contenuto, fino a 120 Crt, è gestito come

stringa di bit unica e continua senza interruzione, sia a livello Crt che registro.

Sorgente o destinazione dei dati, nel nostro caso è la LDR, essa ha un tempo di accesso

di 2,1 mSec. Pertanto o si provvede con un registro di supporto o si dedica una parte del

supporto stesso allo scopo di fornire il tempo di accesso mancante.

In stampa la stessa esigenza è risolta dal settore privo di denti della ruota fonica, che

rendendo disponibile un tempo superiore al tempo di accesso della LDR (2,1 mSec.),

garantisce l’ accesso al Crt in LDR in tempo utile.

Per analogia in cartolina, onde ridurre l’hardware, il problema è risolto con l’inserimento

di 4 bit supplementari nel Crt.

Ogni Crt di cartolina è quindi composto da 12 bit, 8 informazione e 4 di servizio.

21In totale su ogni pista della cartolina vengono registrati 960 + 480 = 1440 bit.

Sistema di registrazione con ritorno a zero (RZ)

I dati su cartolina vengono registrati utilizzando il sistema di ritorno a zero RZ, esso

prevede che ogni periodo di bit abbia almeno una commutazione dovuta al clock.

In registrazione (AP On), il periodo di bit è definito tramite l’oscillatore OR . In ogni

periodo di bit si ha la commutazione iniziale di clock, seguita dalla eventuale

commutazione a metà periodo in caso di informazione di bit = 1.

In lettura, la prima commutazione magnetica, rilevata dalla testina, viene considerata

come clock del 1° bit di informazione. Il clock fa partire il monostabile OS, che ha una

durata pari a 2/3 del periodo di bit.

Le commutazioni magnetiche con OS attivo sono considerate come bit 1.

Le commutazioni magnetiche durante OS passivo sono considerate come clock e come tali

fanno ripartire OS.

Bit di parità

Diagramma Bit di parità.

L’inserimento dei 4 bit di servizio viene utilizzato per provvedere un bit controllo di parità

a livello Crt.

L’informazione da registrare è data da NL, la cui forma d’onda alla fine del Crt (HN), in

caso di numero di bit = 1 pari è reset. Se NL è e set, bit dispari, esso viene resettato

durante il primo bit di servizio che assume la funzione di bit di controllo della parità.

In lettura, viene controllato che il Crt di 12 bit il numero di bit = 1 sia pari, in caso

contrario si attiva la condizione di errore (ER) .

Info su processi fondamentali

L’hardware della Programma 101 non essendo strutturato, rende complicata la lettura dei

fogli logici anche per chi desidera una conoscenza non approfondita del suo

funzionamento.

Quanto segue vuole fornire alcune informazioni su “processi base”, utili anche per

facilitare un successivo approfondimento dei dettagli.

Introduzione dati

I dati sono di due tipi: numerici ed istruzioni di programma.

Essi possono essere introdotti per mezzo di tastiera e cartolina magnetica. La cartolina

tipicamente è utilizzata introdurre il programma.

Dato numerico

Il dato numerico, tipicamente introdotto da tastiera, viene inserito sempre implicitamente

nel registro M.

Esso viene battuto in modo naturale, a partire dalla cifra più significativa.

Nel caso di numero senza decimali, la virgola è comunque sempre sulla cifra delle unità.

Prima che venga battuta, la virgola accompagna sempre l’ultima cifra introdotta, la sua

introduzione ha l’effetto di bloccarne la posizione. L’eventuale cifra seguente costituirà il

valore dei decimi di unità.

Il riferimento,TA in R, indica il carattere precedente quello in cui è scritta la cifra attuale,

le cifre eventuali precedenti sono spostate in blocco di un carattere per farle posto.

Il segno meno può essere introdotto in qualsiasi momento, a partire da prima battuta,

sino a quella che precede il tasto istruzione che chiude la fase dell’introduzione.

A fine introduzione, il dato in M rispetto il riferimento TA in R presenta sul carattere

seguente la cifra ultima battuta, la meno significativa, dopo le cifre interposte chiude le

cifre quella più significativa. Fisicamente il dato può presentarsi a cavallo del gap,

possibile nel caso che il riferimento sia stato spostato dopo l’inizializzazione.

Il dato è sempre visto nella sua interezza, l’informazione di inizio e fine è data da un flip

flop che memorizza la persistenza del bit dato valido (TB) nel registro.

Programma

La fase di introduzione del programma, sia da tastiera che da cartolina, parte sempre dal

1° carattere, del registro che memorizza la 1 a istruzione. Il registro sarà G se programma

utilizzante 5 registri, E se programma parziale 2 registri.

Le istruzioni successive sono inserite nel registro a seguire a partire dal 2° carattere. I

registri seguenti sono interessati a seguito della scrittura nel 24° carattere di quello

attuale. La sequenza G, I, F, E, D è bloccata.

Allineamento registri deposito dati

I registri deposito dati sono B, C, D, E, F se interi, b, c, d, e, f se splittati.

Le istruzioni operano sui registri dati, splittati o interi, senza differenza.

I registri A ed M sono i soli che possono fare scorrere l’informazione in ciclo nei loro 24

caratteri. Lo scorrimento di un carattere è ottenuto , introducendo nel ciclo di richiusura

del registro sulla linea di ritardo, il registro K.

L’allineamento del registro A o M, avviene tra il riferimento di inizio registro ed a seconda

dell’istruzione in alternativa con cifra più significativa o virgola o cifra meno significativa,.

Le istruzioni che scrivono dati nei registri deposito sono solo quelle di trasferimento dal

registro M o di scambio con A. Esse fanno precedere la scrittura del dato da una fase di

allineamento, che pone la cifra meno significativa nel 1° carattere del registro, se intero,

nel 13° carattere se splittato.

Tutte le altre istruzioni che indirizzano un registro deposito, possono leggerlo lasciandolo

invariato o cancellarlo.

Calcolo

I registri interessati dalle istruzioni di calcolo sono A, M, R.

Il registro A contiene tipicamente, all’inizio dell’istruzione il 1° operando ed alla sua fine il

risultato.

Le istruzioni con 2 operandi trasferiscono il registro indicato dall’istruzione in M, 2°

operando, prima di eseguire il processo dell’informazione.

In caso di radice quadrata, il registro indicato dall’istruzione viene prima trasferito in A

poi elaborato.

Tutte

•

•

•

•

•

le istruzioni di calcolo seguono un processo di cinque fasi in sequenza:

Collocamento dei dati di inizio calcolo nei registri.

Allineamento relativo dei registri.

Scrittura riferimento numero cifre decimali.

Ciclo di calcolo.

Formattazione risultato.

L’hardware è in grado di eseguire in un ciclo una somma o sottrazione, tra il dato in A e

quello in M. Se l’istruzione richiede cicli multipli come in moltiplicazione, divisione e radice

quadrata, conta in R il numero di cicli che costituisce per queste istruzioni il risultato.

L’hardware decide in base all’istruzione e al segno degli operandi, l’esecuzione di un ciclo

di somma o sottrazione.

Stampa

La stampante viene utilizzata per:

• Stampa dato e istruzione introdotte da tastiera.

• Istruzioni di stampa.

• Stampa programma.

• Interlinea.

Le diverse stampe e l’interlinea eseguono tutte lo stesso ciclo che comprende:

• Attivazione elettromagnete moto del carrello porta martello.

• Attesa della chiusura micro carrello in moto.

• Attesa da 4 a 28 giri del tamburo – Funzione del dato da stampare.

• Disattivazione elettromagnete moto del carrello porta martello.

• Attesa della apertura micro carrello in moto – Carrello fermo.

La differenza è data dalla eventuale battuta del martello per la stampa di simboli.

La sincronizzazione tra tamburo porta simboli e rotella dentata, ad esempio, il 2° dente si

presenta in coincidenza, ogni giro di tamburo, del primo simbolo. Al 16° dente

corrisponderà il 16 simbolo, ultimo stampabile prima del gap.

Il gap, la cui durata essendo superiore al tempo di accesso alla linea di ritardo, permette

la lettura del codice, istruzione, indirizzo o cifra stampato il giro seguente.

Il codice viene caricato nel sommatore complementato, ad esempio, se si deve stampare

il 1° simbolo il codice sarà 0000 (0 Hex), che complementato diventa 1111 (F Hex). Il 1°

dente incrementa il sommatore a 0000 (0 Hex), causando il riporto sul 4° bit o riporto di

24cifra. Ne segue che per stampare il 6° simbolo, codice 0101 ( 5 Hex), con complemento

1010 (A Hex) avrò un riporto sul 4° bit dopo 6 denti.

Onde assorbire le tolleranze introdotte dalla circuiteria di rilevamento del riporto, si

sincronizza il comando all’elettromagnete di battuta martello attivandola con la fine del

dente che genera il riporto e disattiva con la fine del dente seguente.

Processo dell’informazione - Stati logici

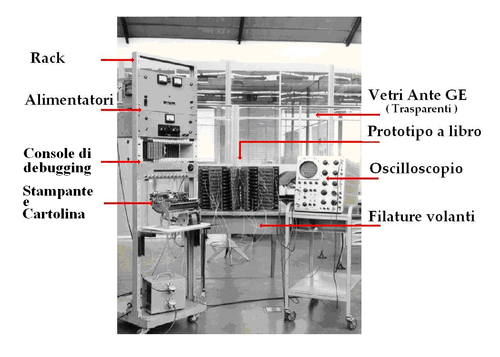

P101- Fogli logici. Foglio 2.

L’elaborazione dell’informazione nell’esecuzione dell’istruzione, è suddivisa in fasi

funzionali denominate stati.

Gli stati sono 15, il nome varia da SA a SS, essi sono tra loro esclusivi e implementati

con flip flop.

La sequenza dei nomi non è sempre indicativa della sequenza di esecuzione.

Sequenza e numero degli stati dipende dalla istruzione e dal modo, manuale o

programma. La durata dello stato, misurata in numero di cicli di LDR, è variabile.

Pure variabile è il punto del ciclo in cui avviene la transizione tra stato e stato,

tipicamente il gap della linea di ritardo o inizio dell’informazione valida nel registro.

Lo stato di posizionamento all’accensione o reset da tastiera è SE.

Con il reset si inizializzano, temporizzazione (scrittura dei bit di servizio base) e registri

M, A ed R con uno zero negativo, dopo tre cicli di linea di ritardo si ha il cambio stato da

SE a SA.

Lo stato SA è segnalato dall’accensione della luce verde fissa, in questo stato il sistema è

in attesa dell’intervento dell’operatore, sia per calcolo manuale, introduzione cartolina,

avvio o prosecuzione del programma.

La fase di attesa intervento dell’operatore termina con la battuta di un tasto istruzione

che resetta SA. Lo stato seguente dipende dal codice della istruzione

Al termine di un calcolo manuale o di esecuzione di un programma, senza errore, si

ritorna sempre allo stato SA con lampada verde accesa fissa.

In caso di errore, si interrompe la sequenza standard degli stati e si forza il ritorno in SA

con lampada rossa accesa fissa.

La fase di lettura o scrittura della cartolina avviene interamente in SA.

Gli stati in genere, sono eseguiti una sola volta per istruzione, tranne le istruzioni di

moltiplicazione, divisione e radice quadrata che richiedono l’esecuzione multipla del ciclo

di stati SF, SG, SH e SK.

Elenco Stati e loro funzione

Trascurando utilizzi non generalizzabili si elencano in ordine alfabetico gli stati e la

funzione che li caratterizza.

SA - Attesa intervento operatore.

Lo stato è raggiunto automaticamente al termine di :

• Fase di inizializzazione (SE).

• Istruzione manuale.

• Esecuzione di un programma.

• Stampa programma.

Lo stato di SA in presenza di lampadino Rosso On, segnala un errore accaduto durante

l’esecuzione dell’ultima istruzione.

L’errore interrompe la sequenza delle istruzioni e pone la macchina in SA.

La condizione di errore è riposta dall’operatore tramite:

• Battuta di un tasto.

• Introduzione cartolina.

• Reset generale.

Le operazioni sulla cartolina avvengono tutte all’interno dello stato SA. Esse sono

caratterizzate dall’impostazione dei pulsanti di modo, AP e AZ, oltre che da SO che

segnala presenza di cartolina sotto testina magnetica.

L’ uscita da SA avviene a seguito della battuta di un tasto istruzione , le istruzioni di salto

e tasto Start avviano il programma.

SB - Preparatorio all’esecuzione dell’istruzione

SB ha una durata tipica di 2 cicli di LDR. NH = 0 indica 1°giro, NH = 1 2° giro.

In SB, in presenza di una istruzione di salto condizionato, si verifica la condizione, A > 0,

prima di passare a SP per l’estrazione dell’istruzione seguente.

Il passaggio ad SP avviene comunque se in presenza di salto o riferimento.

Se l’istruzione è di calcolo, tranne radice, avviene il trasferimento del registro indicato

nell’istruzione in M , tramite SB * ZA * LX * ZK \ * VX \ .

Se radice, il registro con il radicando viene trasferito in A tramite WK * LX, M viene

inizializzato con 1 tramite SB * ZK * NH * TR * (TB+TD+TE).

Il diagramma mostra la preparazione nei registri A ed M in caso di radice con registro

splittato d.

In A viene trasferito, a partire dal 13° Crt, il numero 1234,7 contenuto in d.

Il trasferimento avviene nel 1° giro di LDR.

In M, cancellato nel 1° giro, nel 2° durante TR viene scritto 1.

Diagramma Stato SB. Radice preparazione registri.

27Per le altre istruzioni e un dettaglio maggiore la descrizione è inserita nelle pagine loro

dedicate.

SC,SD - Allineamento registri M ed A

SC e SD servono allineare il contenuto di M e A, rispetto il 1° o 13° Crt di LDR.

La cifra da allineare dipende sia dalla istruzione che registro.

Il numero di cicli è variabile, esso incide notevolmente sulla durata dell’esecuzione

dell’istruzione, può essere ridotto alternando selezione di registri interi con splittati, in

quanto il riferimento per l’allineamento TM, si sposta alternativamente a inizio o metà

registro.

L’allineamento avviene per mezzo di uno spostamento relativo del contenuto di un

registro rispetto gli altri 9 registri. Lo spostamento si ottiene con l’inserimento di un

registro (K) di 1 Crt prima della scrittura in LDR.

Si ha quindi il ritardo di 1 Crt per ogni giro di LDR con K connesso.

Quindi il registro M in SC o A in SD, rallenta e scorre all’indietro, avvicinandosi al punto di

traguardo (TM) a partire dalla cifra più significativa. Ultima cifra del numero nel registro

ad uscire da LDR.

Quando la cifra passa oltre il 24° Crt. si trova riscritta sul Crt seguente dell’anello che è il

1° Crt.

Il passaggio della cifra più significativa traverso il gap è segnalato dal set di NF, tramite il

gate NA*RK*XO.

Il giro seguente le cifre più significative nel registro precederanno quelle meno

significative nella lettura della LDR.

Il meccanismo hardware utilizza il flip flop di temporizzazione TM, che in caso di

operazioni su registro intero, corrisponde al 24° Crt, se splittato al 12°.

Il Crt su cui si decide l’allineamento è dato dal momento del suo ingresso nel registro K,

quindi 1 Crt prima della effettiva scrittura in LDR. A scrittura completata, l’esito è che il

dato si trova allineato sul Crt. successivo (1° o 13° Cr).

A seconda dell’istruzione, l’allineamento di M e A avviene su :

1. Cifra più significativa. Divisione, radice quadra e se A moltiplica.

2. Virgola. Somma algebrica ( + e -) , radice quadra, e se M per moltiplica.

3. Cifra meno significativa. Caso di default, per le altre istruzioni.

28In caso di istruzioni di calcolo, in caso di una sola cifra per la parte intera, l’allineamento

su cifra più significativa coincide con quello sulla virgola.

I due stati SC e SD, sono simili, svolgono le stesse operazioni con oggetto il dato in M e

A. Il periodo di osservazione dell’informazione è dato da PO, che definisce il tempo nel

quale si leggono cifre valide.

PO in stati diversi da SC e SD è l’or di PM e PA, in SC, PO coincide con PM (M) essendo

bloccato PA e in SD con PA (A) essendo bloccato PM.

Il flip flop ND, abilita lo scorrimento del registro attraverso K, esso è settato dal 2° fronte

di PO onde evitare lo spezzamento in due tronconi del numero.

Il flip flop NG, in caso di sovrapposizione iniziale di PO a TM, attende che il registro scorra

sino ad evitare detta sovrapposizione, quindi abilita con XO il traguardo delle condizioni di

allineamento.

Eventuali resti da operazioni precedenti di bit di servizio (TA, TB, TC) “orfani” nel registro,

sono cancellati sino alla lettura del 1° bit di cifra o virgola.

Allo scopo ogni TD in TM si mette in moto il duo NA – NB :

• NA

• NB

Il flip

•

•

•

Pone fine con UI1 (NA*XO*RK) che setta NF, al blocco dei bit di servizio

“orfani”.

Attua con XH1 (NB*CA*NH\) il blocco della scrittura sul Crt seguente dei

bit di servizio.

flop NH viene settato dai segnali di raggiunto allineamento, i quali sono dati da:

Gate 02 A 13

Condizione di cifra più significativa.

Gate 02 A 9 Condizione di virgola.

Gate 02 M 1

Condizione di fine numero.

Lo scorrere in sequenza dell’informazione dei registri nella LDR, fa si che l’accadimento

della prima condizione, se abilitato dalla istruzione, impedisce le altre.

Lo stesso vale per la seconda condizione nei confronti della terza.

NH stesso con il giungere del 1° fronte di PO genera YD da cui MS e quindi il cambio

stato.

SE - Funzione multiple

SE ha una durata tipica di 2 cicli di LDR. Lo stato di NH = 0 indica 1°giro, NH = 1 2° giro.

In inizializzazione,1° stato eseguito, SE dura 3 cicli di LDR.

Le sue funzioni principali sono:

Al Power On, scrive i bit di servizio in B e C che delimitano i confini di LDR e split. Inoltre

pone un -0, sul 24° Crt dei registri M, A ed R.

Se istruzione di calcolo, scrive in A il TA che precede la virgola del numero di Crt

impostati nella rotella decimali.

Se istruzione di trasferimento lo attua nel suo 2° ciclo.

Per le altre istruzioni ed un dettaglio maggiore la descrizione è inserita nelle pagine ad

esse dedicate.

SF,SG,SH,SK,SL - Esecuzione istruzioni di calcolo

Tutti gli stati del gruppo durano 1 ciclo di LDR.

Lo stato SL, ultimo del gruppo viene eseguito una sola volta e conclude il calcolo.

SF, SG, SH, SK compongono un ciclo e sono eseguiti in sequenza.

In somma e sottrazione il ciclo viene eseguito una sola volta.

Nelle altre istruzioni il numero di cicli dipende dal numero di cifre e dal loro valore.

In moltiplica l’uscita dal ciclo con il passaggio a SL avviene dopo SK, in divisione e radice

dopo SF.

In radice il numero di cicli è raddoppiato.

La funzione tipica degli stati nel ciclo di calcolo è:

SF

SG

SH

SK

Verifica se M > A.

Somma 1 al contenuto di R.

Esegue la somma algebrica tra M e A.

Corregge il risultato della somma algebrica.

Ogni istruzione di calcolo termina con lo stato SL che ha la funzione di formattarne il

risultato.

SM,SN,SS - Riservati alla stampa

La sequenza degli stati di stampa è fissa a SM, segue sempre SN quindi SS. La sequenza

è innescata da :

• SA

Tutte le istruzioni tranne che di stampa.

• SE

Istruzioni di stampa.

• SP

Stampa programma (AZ).

Funzione dei singoli stati:

• SM

Stampa simbolo istruzione, registro e spazio distanziatore.

• SN

Stampa dato numerico.

• SS

Attesa del carrello di stampa a riposo.

Con stampa di 30 Crt/Sec. La stampa di un simbolo necessita di 33,33 mSec.

Il carrello di stampa è messo e tenuto in movimento da CD, or di SM e SN.

La durata di SM è quasi costante, essendo la variabilità, dovuta al sincronismo tra

posizione istantanea del tamburo e comando stampa. Costante è il tempo di 100 mSec. di

stampa dei simboli indirizzo, istruzione e spazio.

SN ha durata proporzionale al numero di cifre da stampare a cui vanno aggiunti virgola e

segno.

SS ha una durata funzione del tempo di ritorno a casa del carrello di stampa indicato dal

μswitch AW.

Nel caso di stampa forzata del risultato del calcolo di moltiplicazione, divisione e radice, a

seguito della forzatura del codice di stampa A (84H), la sequenza segue la modalità

standard.

Unica eccezione, esecuzione da programma dell’istruzione Azzera Registro (*), lo stato

SS, segue SE mediante YX ( SE * ZL * HE * HP ). In questo caso l’istruzione non

comporta movimento del carrello.

SP - Fetch istruzione di programma

SP ha la funzione di estrarre il codice dell’istruzione da eseguire caricandola nel registro H

.

Lo stato SP è raggiunto nei casi di :

• Fine esecuzione istruzione data da YT, se HP = 1 esecuzione programma.

• SB Salto o riferimento di salto.

• SE Istruzione S di start programma.

• SD Stampa programma.

SP ha una durata di 2 - 6 cicli di LDR. Il numero di cicli massimo si ha con il riferimento di

salto posizionato nel 5° registro.

Se l’istruzione estratta è S (0) si ha il reset di HP, stop all’esecuzione del programma ed il

rientro in SA

SO - Cartolina nel trascinatore

SO deriva dalla “squadratura” del segnale da Switch AO attivato dal passaggio sotto la

testina magnetica della cartolina.

Dispositivi di interfaccia utente fisici

Tasto accensione

31Il tasto è posto, fronte macchina, in basso a destra.

Foto. Tasto Accensione

Alla sua impostazione si applica la tensione alternata all’alimentatore.

L’alimentatore fornisce le tensioni continue che garantiscono il corretto funzionamento sia

dei circuiti in cassettiera che quelli delle attuazioni comandi verso la meccanica.

Lo stato di inizializzazione macchina minimo è garantito da un flip flop (SR).

Nella fase di stabilizzazione delle tensioni continue, SR sbilanciato da una rete RC, si setta

e agendo sui flip flop base, blocca possibili azioni casuali.

L’azionamento del tasto di reset pone SR = 0.

Tasto Reset

Il tasto, incorporato nelle tastiera è il primo in alto a sinistra.

Foto. Tasto reset.

Il tasto di Reset genera 2 cicli di tastiera:

• 1° Aziona il μSwitch AG

• 2° Aziona 2 μSwitch AT e AK

Reset generale.

Avvio temporizzazione + strobe Crt.

Sul tasto di reset non agisce il blocco meccanico della tastiera.

L’azionamento del Reset, provoca la inizializzazione della P101 mediante la scrittura nel

registro B e C dei bit di servizio (TA) che gestiscono la temporizzazione base.

Nei registri M, A, R è posta la cifra -0 sul 24° Crt.

I registri deposito e programma, hanno tutti i bit a zero, tranne quelli utili alla

temporizzazione.

Tastiera

La tastiera costituisce il dispositivo primario di introduzione dati nella P101.

Foto. Tastiera.

32La tastiera dispone di 37 tasti.

Reset generale (1).

Dato numerico (12). Cifre, virgola e meno.

Clear (1).

Indirizzi di registro (7). A, R, B, C, D, E, F .

Registro splittato (1).

Istruzioni (10).

Start (1).

Salti programma (4).

Tutti i tasti attivano 1 ciclo meccanico, il Reset 2.

Il ciclo meccanico originato dalla pressione sul tasto agisce su 12 μswitch :

• AG

Reset generale.

• AT

Individua 2° ciclo di reset.

• AK

Strobe Crt pronto.

• AA – AD

Codice dato numerico / Indirizzo / Istruzione.

• AE

Indirizzo.

• AF

Indirizzo / Istruzione.

• AM

Segno meno in dato numerico.

• AN

Azzera dato. Se premuto prima di tasto Istruzione.

• AV

Virgola.

I μswitch AE, AF, AK, AN, AT forniscono in uscita segnali diritto e negato.

La virgola e il segno meno non attivano il μswitch di strobe Crt valido AK.

Il ciclo meccanico dopo aver commutato i μswitch li lascia impostati sino al ciclo seguente

ad eccezione del μswitch di strobe AK che ritorna a riposo.

AN Clear ha l’effetto di azzerare M , predisponendolo a un nuovo dato.

Foto μSwitch Tastiera e Trascinamento cartolina.

La cifra introdotta mediante un tasto numerico viene inserita nel Crt della LDR

corrispondente al TA di R, le cifre precedenti, se presenti vengono ritardate di un Crt.

I tasti virgola e meno, non essendo accompagnati da uno strobe di Crt, non originano un

ciclo di inserimento Crt in LDR.

L’informazione dei due tasti è posta in bit dei Crt introdotti precedentemente, TC per

segno meno e TD per la virgola.

In caso di battuta di segno meno, sono posti a 1 i TC di tutte le cifre valide.

Il dato è introdotto a partire dalle cifre più significative, il bit TD specificante la posizione

della virgola rimane sul Crt, individuato dal TA in B, sino alla battuta del tasto virgola.

La battuta della virgola, fissando la posizione della cifra di peso 10 0 (unità), fissa il TD alla

cifra che l’ ha preceduta.

La battuta di altri tasti cifra, procura lo spostamento di tutta l’informazione introdotta

prima , bit TD di virgola compreso.

Durante il tempo in cui la macchina non è in attesa di dati la tastiera è bloccata tramite

elettromagnete.

In caso di più tasti contemporanei la tastiera si blocca meccanicamente.

La tastiera permette la battuta in successione di due tasti senza l’intervento del blocco

meccanico.

A fianco dei pulsanti di modo è posto il tasto di sblocco meccanico tastiera.

34In Appendice A. Codici da tastiera si trova il dettaglio dei codici attribuiti ai tasti.

Lampadini

Il sistema, mediante lampadini, comunica all’operatore lo stato di:

•

•

•

Attesa introduzioni dai o programma. Luce verde fissa.

Programma in esecuzione.

Luce verde intermittente.

Condizione di errore.

Luce rossa fissa.

Pulsanti introduzione - stampa programma

I pulsanti “bistabili” di modo introduzione o stampa programma sono 2:

•

•

Registra Programma

Determina la scrittura delle istruzioni nei registri

.

programma. Input tastiera o cartolina.

Stampa programma

Seguito da istruzione S o salto, comanda la stampa

del programma nei registri.

Foto. Pulsanti di modo.

Le istruzioni possono essere introdotte sia da tastiera che da cartolina.

La lettura o scrittura delle istruzioni in LDR è sequenziale e fissa.

Inizia dal registro G seguono I, F, E , D fino a un massimo di 120 istruzioni.

La lettura della cartolina avviene con macchina in attesa, luce verde fissa, tastiera

sbloccata ed introduzione della cartolina.

Programma corto

L’impostazione di entrambi i pulsanti restringe a E, D i registri

coinvolti nelle operazioni di lettura e scrittura.

Le istruzioni sono massimo 48.

Gli altri registri restano immutati.

La battuta del tasto della prima istruzione o il passaggio della cartolina provocano la

cancellazione dei registri di programma.

Sblocco Tastiera, sblocca la stessa tastiera nel caso di blocco meccanico per battuta

contemporanea di più tasti.

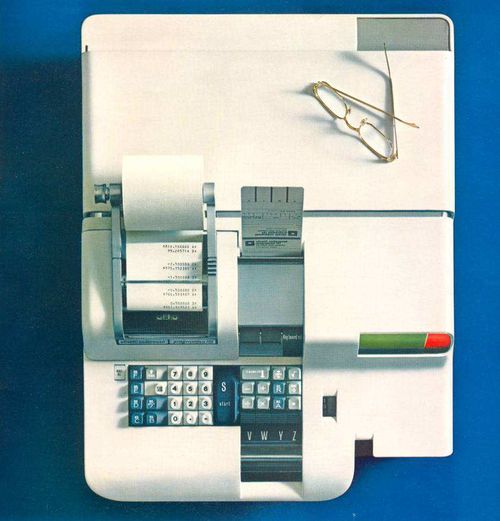

Stampante

La stampa avviene con movimento del carrello da destra a sinistra.

Il ciclo di stampa registro comporta automaticamente una interlinea, ne segue che ogni

riga di stampa contiene un solo dato. Il fine ciclo prevede il ritorno alla posizione di

partenza del carrello.

È disponibile l’istruzione di interlinea singola, non quella di tabulazione carrello.

Foto. Gruppo stampa.

Il gruppo di stampa è formato da :

# Tamburo cilindrico portante in rilievo i caratteri in rotazione continua. I caratteri corrispondono ai simboli delle istruzioni, indirizzi, cifre numeriche, virgola e segno meno. Il numero di colonne sul tamburo è 28, la 1 a riservata all’istruzione, la 2 a all’indirizzo, le altre alle cifre, segno meno e virgola. La 3 a colonna non è comunque mai utilizzata, producendo la separazione tra istruzione-indirizzo e dato numerico.

Il numero di cifre massimo stampabili, sottratti segno e virgola è 23. Il numero di righe di simboli sul tamburo è 24. Le prime 16 righe di simboli sono utilizzate. Le 8 restanti righe di simboli hanno lo scopo di equilibrare il tamburo in rotazione.

# Rotella dentata, in rotazione solidale con il tamburo. La variazione di flusso magnetico, data dal passaggio del dente in

corrispondenza di una bobina origina un segnale il cui passo angolare è uguale a quello dei simboli sul tamburo.

La rotella fornisce quindi l’informazione che sincronizza posizione del martelletto e simboli sul tamburo. Il numero di denti della rotella è 17.

I denti non sono distribuiti sull’intera circonferenza della rotella, ma ne lasciano un settore libero. Il tempo di rotazione corrispondente al settore senza denti, fornisce il tempo che permette l’accesso alla LDR per il prelievo

del Crt. da stampare.

# Carrello porta martello di battuta, comandato da elettromagnete, dotato di moto continuo rettilineo parallelo all’asse maggiore del tamburo porta

caratteri. Il carrello avanza di un passo Crt ad ogni giro del tamburo.

# Martelletto di stampa di un simbolo a battuta, solidale al carrello, anche esso

comandato da elettromagnete. Onde recuperare i ritardi circuitali variabili tra il momento di rilevamento del dente e il set del flip flop che abilita la battuta, si è inserito un flip flop di servizio onde assicurare sincronismo e tempo costante di battuta.

Appendice C. Tabella di corrispondenza tra simboli e denti.

Rotella decimali

Il calcolo avviene con virgola naturale.

Il numero di decimali con cui viene normalizzato il risultato delle istruzioni aritmetiche e la stampa da programma, è quello impostato tramite una rotella impostata manualmente. La scelta possibile è 0 – 15 cifre decimali.

In introduzione manuale , il dato viene stampato con il numero di cifre decimali introdotto

dall’operatore.

Foto. Rotella decimali.

Cartolina

La cartolina è il supporto per il trasporto dei programmi della P101.

L’operatore posizionando il pulsante Stampa Programma, sceglie tra 2 formati di

cartolina:

• Intero

120 Crt

5 Registri G(1), I(2), F, E, D.

• Ridotto

48 Crt 2 Registri E,D.

Il programmatore oltre le istruzioni. ha la possibilità di inserire nei registri di programma

dei numeri.

Le tecniche utilizzate sono descritte in P101 Manuale di programmazione P101.

L’esecuzione di un programma può prevedere l’inserimento di più cartoline in tempi

diversi.

Foto . Inserimento Cartolina.

Ogni pista ha la capacità massima di 5 registri programma, 24 X 5= 120 Crt.

La testina di lettura – scrittura della cartolina non coincidente con l’asse del supporto,

permette mediante semplice capovolgimento della cartolina, il riutilizzo dello stesso

supporto per altre 120 istruzioni.

La faccia del supporto non ricoperto da ossido magnetico è divisa orizzontalmente in due

parti uguali, con scritte speculari fornenti lo spazio a un breve memo relativo ai due

programmi registrati.

Struttura fisica dell’unità di calcolo

Cassettiera

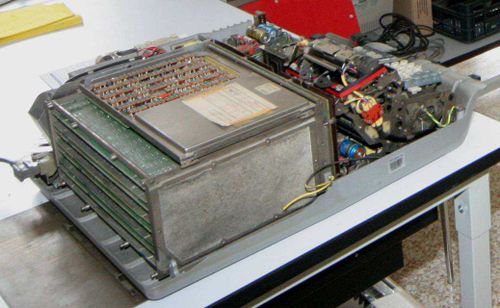

La struttura della cassettiera è di lamiera aperta sul lato posteriore per permettere

l’inserimento delle piastre.

Sul lato posteriore è, fissato con viti il circuito stampato del back panel.

Foto. Cassettiera.

Per ottenere una riduzione in altezza, le piastra pari sono inserite capovolte in modo che

le colonne dei micromoduli della piastra pari scorrono tra le colonne delle piastre dispari.

La cassettiera accoglie 9 piastre, la prima piastra NR. 1 è quella in basso, l’ultima la nona,

in alto, è una piastra ridotta per poter essere affiancata dalla linea di ritardo (LDR).

La piastra 9° ridotta, metà colonne ed un numero ridotto di righe, permette alla

carrozzeria di essere più bassa in coda e quindi appaia più corta.

L’inserimento delle piastre è facilitato da guide laterali.

Il raffreddamento delle piastre in cassettiera è data da una ventola azionata mediante

cinghia dal motore unico di macchina.

Back panel

Foto Intercablaggi P101.

Il circuito stampato monta 34 connettori a 28 contatti, disposti su 9 righe e 4 colonne. La

9 a riga, in figura monta solo 2 connettori.

Alla base del back panel, in orizzontale sono saldati i pin di connessione “maschi” di 4

connettori a 12 vie per i segnali ai circuiti attuatori di stampante, tastiera, cartolina.

Appendice B. Connettori Pacco Elettronica – Attuazioni.

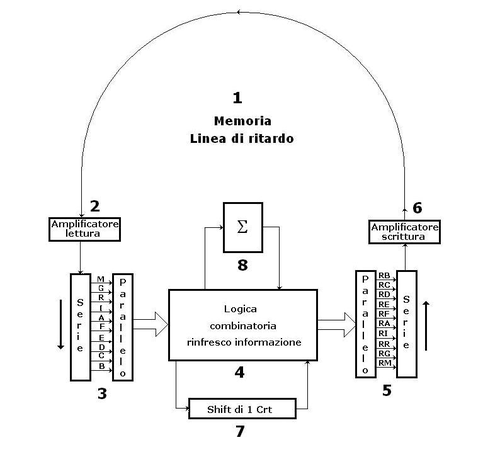

Memoria – Linea di ritardo

Foto. Linea di ritardo.

Il tipo di memoria usato è una linea di ritardo realizzata utilizzando le proprietà

magnetostrittive di un filo d’acciaio armonico.

41L’informazione è contenuta nella successione delle torsioni inflitte al filo dal circuito di

scrittura nella linea di ritardo (LDR). In caso di bit posto a 1 (ON). la forma d’onda di

scrittura ha una commutazione a metà del periodo di bit.

Il mezzo è quindi ad accesso strettamente sequenziale con un tempo di latenza

proporzionale alla lunghezza del filo d’acciaio. Grado di parallelismo 1 bit.

Data una frequenza di scrittura di 1 MBit / Sec , una capacità totale è di 1920 Bit e un

gap per incorporare le tolleranze nel sistema elettro meccanico, si ha un tempo di riciclo o

latenza di 2,1 mSec .

La linea di ritardo con un piastrino con il circuito di amplificazione di lettura, per

protezione è inscatolata in una struttura di lamiera.

Una cornice di metallo fornisce la struttura per il montaggio affiancato della LDR e di una

semipiastra da inserire nella 9° posizione della cassettiera.

Il circuito è suddiviso in tre blocchi funzionali: l’amplificatore del segnale generato dal

trasduttore elettromagnetico, uno squadratore ed un generatore di impulso di durata di

0.5 μSec.

Descrizione LDR a cura di Alessandro Graciotti

Schema a blocchi amplificatore Linea di ritardo.

L’amplificazione del segnale di ingresso è effettuata da un amplificatore differenziale a

due stadi NPN-PNP (T6 – T9) seguito da un circuito di uscita NPN single-ended (T1). Il

trasduttore è collegato all’ingresso non invertente dell’amplificatore; il segnale di uscita è

retrocesso sull’ingresso invertente, interamente per la componente continua, attenuato di

circa 400 volte per la componente alternata. Il guadagno open-loop calcolato

dell’amplificatore è di circa 500; per effetto della contro reazione il guadagno effettivo in

ac risulta quindi essere di circa 220 (confermato dalle misure).

Il ritorno del filtraggio del feed-back (C4 e C5) è collegato con il ritorno del trasduttore ad

una tensione costante di circa +9V ricavata con lo zener Z2 (1N756) in serie ad un diodo,

in questo modo un eventuale rumore presente sull’alimentazione non verrà amplificato

42essendo presentato in modo comune sui due ingressi. La tensione di uscita a riposo si

stabilizza, per effetto della contro reazione totale in dc , allo stesso livello dell’ingresso.

Il segnale amplificato pilota un classico trigger di schmitt (T4 T5) la cui soglia è

posizionata a circa 7V cioè due volt al di sotto della tensione di uscita a riposo

dell’amplificatore; l’isteresi è di circa 1V. La tensione al trasduttore necessaria a eccitare il

trigger di schmitt risulta quindi essere di circa -8mV. L’uscita dello squadratore è un

segnale positivo di circa 5V la cui durata dipende dalla forma del segnale di ingresso.

Il segnale squadrato pilota un oscillatore monostabile di 500nS costituito da T2 e T3.

L’uscita dell’ univibratore è di circa 12V senza carico.

Piastra

Foto. Piastra.

La piastra è supporto di circuito stampato a uno strato su 2 facce.

Le tracce sulle 2 facce sono connesse tramite fori metallizzati.

I componenti, micromoduli, sono montati solo sulla faccia superiore.

La piastra permette di montare i micromoduli disposti su 12 colonne.

Il numero di micromoduli per colonna non è fisso, in quanto gli stessi hanno dimensioni

diverse, 2 / 4 righe.

La sbrogliatura dei circuiti stampati è stata fatta manualmente.

Le piste sono state tracciate mediante incollamento manuale di nastrini.

La posizione di montaggio dei micromoduli sulla piastra è data da una lettera identificante

la colonna (A – Q ) e da un numero ( 1- 32) per la riga.

La posizione riportata sui fogli logici, nella documentazione, è quella della 1° riga

occupata dal micromodulo, indipendentemente dal verso, diritto o capovolto, del suo

inserimento nel circuito stampato.

Ad esempio la scritta 04C21, indica piastra 4,colonna C riga 21.

43La connessione tra piastre tramite back panel è permessa da 4 tenoni, disposti sul lato

maggiore in basso del circuito stampato, ognuno di essi riporta 28 madonnine dorate.

| Il totale dei punti di connessione è 28*4= 112.

|

| I piedini 1 e 2 del 1° connettore sono sempre connessi a massa

|

|

I piedini 3 e 4 del 1° connettore sono sempre connessi a +20 Volt.

|

Le operazione di manutenzione dispongono di un tenone, posto sul lato maggiore, in alto

a sinistra, con 8 madonnine dorate.

Con vista piastra lato componenti, la numerazione di colonne, tenoni e delle madonnine

parte sempre da destra

L’inserimento capovolto delle piastre pari comporta anche quello dei segnali sul circuito

stampato del back panel.

| Occore panel |

quindi distinguere , per le piastre pari tra documentazione di piastra e back

|

Nota.

In Olivetti, il primo tentativo di sbrogliatura di circuito stampato complesso è stato fatto a

Pregnana Milanese dall’ing Lerda.

La piastra utilizzata era la piastra della temporizzazione della Programma 101.

Micromodulo

Foto. Micromodulo.

Il micromodulo è “l’invenzione” che ha anticipato i circuiti integrati i cui primi prototipi

sono stati presentati alla stessa mostra, BEMA di NEW YORK, a cui era la P101 in prima

mondiale la P101.

Esso permette un montaggio, su linea separata dei componenti discreti, transistor, diodi,

condensatori e resistenze su un piccolo circuito stampato portante inciso il codice

micromodulo

Il circuito stampato del micromodulo dipende dal circuito realizzato e riporta una sigla

identificativa dello stesso.

Esso ha sempre 2 colonne, il numero di righe 2 / 4, dipende dal circuito.

I componenti discreti sono montati in verticale, lasciando un reoforo libero da inserire

sulla piastra madre.

I micromoduli di 2 righe montano tipicamente resistenze usate come zavorre, riduttrici di

tensione dei segnali e quindi dei disturbi indotti.

Quelli di 4 righe sono tipicamente circuiti NOR, 4 / 5 Ingressi.

Il transistor tipico utilizzato è il 2N708 o equivalente 1W8723. Il diodo è l’ OA95.

Raccolta Circuiti Elettrici.doc

Parte 2 – Struttura Hardware

Temporizzazione dettaglio

Lo schema dei circuiti è in P101- Fogli logici. Foglio 1.

L’hardware della temporizzazione è composto da:

| Oscillatore OT. |

Frequenza base 1 MHz.

|

| Registro shift ML – MP. |

Assegna l’informazione da LDR a banchi di 5 registri.

|

| Flip flop MT. |

Aggiunge un 2° banco di registri.

|

| Flip flop MK. |

Individua il periodo di lettura da LDR del bit nei 10 registri. Frequenza base/10.

|

| Registro shift TA – TH. |

Periodo di Crt. Richiuso ad anello TH su TA. Frequenza base/10/8= 12,5 KHz.

|

| Flip flop TK. |

Periodo del Crt . Set in TA – TD.

|

| Flip flop TT. |

Abilita oscillatore OT. Settato dalla lettura 1° TA di B. Resettato dalla scrittura dell’ultimo bit del 24° Crt di M in LDR.

|

| Flip flop TR. |

Settato dal 2° TA di B. Inizio del 24° Crt. Reset in TT \.

|

| Flip flop TS. |

Set da fine TH del 24° Crt. Reset con scrittura 1° TA in B. Copre la temporizzazione priva di TA – TH.

|

Diagramma Ciclo di temporizzazione .Stato SE.

La temporizzazione è generata da un hardware progettato per essere realizzato con un

numero minimo di componenti.

I confini della memoria sono stabiliti mediante bit di servizio TA scritti in B, l’accesso è

sequenziale, pertanto non è necessario disporre di un contatore hardware specifico dei 24

Crt.

La scansione del tempo è data dall’oscillatore OT (1 MHz).

OT pilota uno registro shift di 5 Bit (ML – MP) connesso ad anello per tutto il tempo di

attività della temporizzazione.

Ad ogni set di ML si ha una commutazione del flip flop MK, il quale con la frequenza 1\10

di quella di bit, indica il tempo di bit per i 10 registri interlacciati.

MK , ad ogni suo fronte di salita, determina lo scorrimento del registro ad anello TA – TH

(8 Bit). Il periodo del registro determina quello di Crt, essendo i registri interlacciati

racchiude 80 Bit.

Il flip flop TK, set con TA, indica bit di servizio o di selezione del registro (TA – TD). Reset

con TE, indica il codice della cifra numerica o dell’istruzione (TE – TH).

I flip flop che memorizzano i bit di registro sono divisi in 2 banchi.

| 1° Banco registri |

B, C, D, E, F

|

| 2° Banco registri |

A, I, R, G, M

|

Il flip flop MT set attribuisce i bit nel registro serie in uscita della LDR al 1° banco di flip

flop. Con MT reset, i bit nel registro serie saranno attribuiti al 2° banco.

I flip flop serie in uscita alla LDR sono 4 (ME , MF, MG, MH ), avendo ogni banco 5

registri, l’informazione relativa al 5° registro del banco è caricata “al volo”

rispettivamente in F e M.

Il momento di informazione nel registro pronta è definito dal flip flop MP.

| MP con MT set (MR), attribuisce l’informazione del registro serie al 1° banco.

|

| MP con MT reset (MX), attribuisce l’informazione del registro serie al 2° banco.

|

MR precede MX di 5 μSec, avendo entrambi un periodo di 10 μSec.

Ne segue che l’informazione valida appartenente allo stesso bit, permane nei 2 banchi

contemporaneamente per soli 5 μSec.

Diagramma Temporizzazione - 1° Ciclo di Linea di ritardo. Vedere al 300-500%.

Gap della Linea di Ritardo

Essendo la memoria fatta di filo d’acciaio, è necessario che una parte di filo sia aggiunta

per assorbire le tolleranze di sistema. Si genera quindi un tempo (Gap) tra la scrittura

dell’8° Bit del 24° Crt in M e la rilettura del 1° Bit del 1° Crt di B.

Durante il periodo di gap l’oscillatore OT è bloccato.

Il flip flop TT definisce il periodo di attività dell’oscillatore base OT.

Durante TT si sovrappongono 3 tipi di attività necessarie per la lettura e scrittura

dell’informazione nella LDR.

- Trasformazione da serie a parallela di 1 Bit per banco dell’informazione.

- Elaborazione dell’informazione dei registri.

- Trasformazione da parallela a serie di 1 Bit per banco dell’informazione.

L’ attività 1, precede del tempo di lettura dei bit del 1° banco di registri (5 μSec), il

possibile utilizzo del banco di registri interessato.

L’attività 2, dispone di 10 μSec per l’elaborazione dell’informazione.

L’attività 3, segue la 2 e si conclude 5 μSec dopo l’attività 2 con la scrittura del 2° banco

di registri.

La fase 2 è pertanto preceduta, inizialmente, da un periodo di tempo di lettura del 1°

banco e seguita alla fine, da un periodo di scrittura del 2° banco di registri in LDR.

In questi 2 periodi, iniziale e finale, l’informazione non è valida, pertanto la

temporizzazione di Crt fornita dal registro TA – TH è bloccata.

Il flip flop TS copre i momenti, iniziale e finale, di non validità dei dati nei registri.

Il flip flop TR, essendo settato dal TA in B posto sul 24° Crt, indica inizio della fase di fine

temporizzazione. Ultimo ciclo TA – TH.

Diagramma Fine Ciclo Linea di ritardo.

Ciclo di rinfresco dell’informazione in LDR

Si è in un ciclo di rinfresco dell’informazione dopo che la macchina ha eseguito un ciclo di

reset ed è in attesa che l’operatore dia il via a qualche operazione.

Questa è la condizione al termine dell’esecuzione sia di comandi manuali che di

programmi.

In questo caso, ogni 2,1 mSec circa, l’informazione nella LDR compie un ciclo in cui viene

ogni volta rinnovata.

La sequenza degli eventi è:

- 1° Bit da LDR dopo il gap setta TT .

- TT sblocca l’oscillatore OT .

- OT avvia il registro di temporizzazione di bit ML – MP.

- ML comanda la commutazione di MK. MK segnala che il bit in B, C, D, E, F, A, I, R, G e M è pronto.

- MK comanda lo shift del registro TA – TH. Il registro TA – TH provvede la temporizzazione di Crt.

La temporizzazione sincronizza l’informazione da linea di ritardo con i flip flop di registro

facente parte di (3) in Figura 1.

La logica combinatoria (4), con la macchina in attesa di azione dell’operatore, copia

l’informazione di bit in (3), nel registro di uscita verso LDR (5) .

Diagramma Ciclo Linea di ritardo

La temporizzazione avviata dal 1° bit letto da LDR , che per settaggio hardware è attribuito al registro B, prosegue in modo ciclico, per il tempo corrispondente a 23 caratteri. Nello slot di tempo corrispondente al bit TA del 24° Crt di B, viene letto il bit che con il set del flip flop TR segnala l’ultimo Crt del ciclo.

- Il 2° bit in TA di B setta TR . Ultimo Crt del ciclo.

- TR abilita al termine di TH il set di TS . Fine del 24° Crt .

- TS scritti gli ultimi bit nel serializzatore in LDR resetta TT .

- TT resettato, blocca OT e quindi tutta la temporizzazione da lui derivante.

- Il blocco della temporizzazione provoca un periodo di attesa (Gap), pari al tempo necessario al 1° bit di B di giungere alla fine del filo di acciaio e di riavviare la temporizzazione per un nuovo ciclo.

La durata della temporizzazione dipende da posizione e presenza del 2° bit in B.

Una sua anticipazione determina una numero di Crt minore di 24.

Con la sua scomparsa la temporizzazione non si arresta determinando la mancanza di gap

ed una perdita di sincronismo con i dati in LDR.

Registro K

Lo schema del circuito è in P101- Fogli logici . Foglio 3.

Il registro K, composto da 8 bit ( KA – KH ) ha la funzione di :

- Contatore di Crt in inizializzazione della temporizzazione e numero decimali.

- Contatore dei denti della ruota fonica in stampa.

- Interfaccia di dati numerici ed istruzioni con:

- Tastiera.

- Stampante.

- Cartolina.

- Allinea il registro selezionato ritardandolo di un Crt per ogni giro di LDR.

- In calcolo contenendo il Crt utilizzato precedentemente nel sommatore, in caso di riporto permette l’inserimento di un TA che segnalerà il Crt durante il ciclo seguente per la correzione della cifra.

Nelle funzioni di conta o di calcolo, con il registro K connesso al sommatore,

l’informazione utile è quella di digit ed è nei 4 bit KE – KH.

Il clock del registro K viene generato da:

- MX tranne che durante la lettura o scrittura cartolina.

- OS , clock di bit cartolina per i soli 8 bit di codice istruzione.

Il clock è continuo tranne che nei 2 casi seguenti :

a) In stampa sulla seconda colonna dell’indirizzo, TK blocca i primi 4 bit, per caricare in

KE – KH il codice dei primi 4 bit del Crt contenente l’indirizzo.

b) Durante la fase di scambio Crt con la cartolina, nel periodo di lettura o scrittura dei 4

bit di servizio aggiuntivi, si inserisce MX per 8 bit abilitati da NB, per scambiare il Crt con

la LDR.

Il dettaglio dell’utilizzo del registro K è inserito nel contesto di descrizione relativo alla

specifica funzione.

Registro H

Lo schema del circuito è in P101- Fogli logici . Foglio 3.

I bit del registro H sono 8 ( HA – HH ).

In esecuzione istruzione contiene il codice dell’istruzione. Tipicamente i bit del registro

indicano:

| HA – HC |

Registro.

|

| HD |

Split.

|

| HE – HH |

Istruzione.

In lettura / scrittura programma o cartolina, seleziona il registro di programma

contenente le istruzioni.

Multiplexer registri

51I circuiti multiplexer sono utilizzati per convogliare su un segnale unico il contenuto di

più registri. L’informazione del segnale sarà quella del registro selezionato dalla

istruzione in esecuzione.

La figura mostra l’utilizzo dei registri dati B, C, D, E, F e dei registri programma G, I ed

eventualmente F, E, D.

La tecnica è resa possibile in quanto le istruzioni prevedono la possibilità di selezionare un

solo registro per istruzione, oltre se utile, un secondo selezionato in modo implicito e

comunque predeterminato in funzione dell’istruzione.

LN, RN, LT - Multiplexer registri dati e programma

image

Il flip flop LN , set con MM*MK e reset con MX, ha la funzione di ritardare il contenuto dei

registri del 1° banco, B, C, D, E, F, riallineandolo al contenuto dei registri del 2° banco, M

ed A e rende possibili le istruzioni di calcolo, trasferimento. Lo stesso rifasamento viene utilizzato per la stampa dei simboli istruzione ed indirizzo o input output verso cartolina, senza dover badare al banco di appartenenza del registro

interessato.

LT – LX viene utilizzata per la stampa del dato numerico.

Nelle istruzioni di calcolo, durante lo stato SB, LT – LX serve per trasferire il registro

selezionato nell’operando implicito M.

RN nelle istruzioni di trasferimento trasporta il segnale del registro selezionato tra i

registri B, C, D, E, F sostituendolo alla richiusura del dato precedente.

LP - Multiplexer registri programma

I registri programma D, E, F, appartengono al 1° banco, mentre G ed I al 2°. Il flip flop LP provvede al riallineamento dell’informazione contenuta nel registro selezionato del 1° banco alla temporizzazione dei registri del 2° banco.

Il flip flop LP viene utilizzato per la lettura dell’istruzione (fetch), durante SP.

image

Reti logiche

CX – OR di stati

image: P101- Fogli logici. Foglio 2

OR logici di stati sono utili per utilizzare le parti hardware utilizzate in fasi diverse della

stessa istruzione o in istruzioni diverse.

Si fornisce l’elenco e gli stati che li originano . Onde semplificare l’hardware, un OR di

stati logici può avere come suo ingresso un altro OR di stati logici.

| CA |

SC, SD, SE.

|

| CB |

SE, SG, SH, SM, SN.

|

| CC |

CH, SE, SM, SN.

|

| CD |

SM, SN.

|

| CE |

SF, SH .

|

| CG |

SA, SB, SC .

|

| CH |

SF, SG, SH, SK .

|

| CK |

SM, SN, SP, VX .

|

| CM |

SB, SE .

|

| VX |

Originato da SB * ZH * HD * DA, indica stato SB in esecuzione istruzione di costante da programma.

|

MS – Cambio stato

document: P101- Fogli logici. Foglio 2.

MS fornisce il segnale che temporizza il passaggio di stato.

MS pilota tutti i reset dello stato attuale tranne SS, attuato da SS * TT \ * VP \ .

Lo stato di destinazione dipende sia dallo stato di provenienza, esso può essere senza alternative come da SH a SK, o dipendere da condizioni anche multiple, vedi SE che può essere seguito da SA, SF, SM, SP, SS.

VA

La rete logica VA viene utilizzata per scrivere il segno meno nei registri A e R nella

formalizzazione risultato, stato SL.

• Nelle istruzioni di moltiplicazione, divisione e radice, ZC * LR * TK \ trasferisce R in

A, bit TE – TH del risultato.

• Tramite SE * ZG * NH (rete RA), forza WK che abilita XC, contenuto di A durante

l’istruzione di scambio registro. ( WK * HF * LA * WA \ ) .

• Se il decodificato di M è attivo, ZG * DM * VA * NK \ ,introduce in SE A in M.

Ricordando che nelle operazioni di calcolo i flip flop :

NK

Set ha il significato di A negativo.

NL

Set ha il significato di segno in A ed M discorde.

Il segno del risultato viene introdotto in VA da:

ZC * NL * TC

Moltiplicazione, divisione con segno discorde.

ZB * NK * NM \ * TC

Somma algebrica A negativo e A > M.

ZB * NK \ * NM * TC

Somma algebrica A positivo e A < M .

La richiusura sui registri A ed R tramite VA è fatta da:

SL * PA * VA * NC

Registro A.

SL * PA * VA * ZF \ * ZK \

Registro R.

XX

XX è usato per commutare NL, flip flop fornente in cartolina, la forma d’onda da registrare

o il bit letto.

In registrazione cartolina:

OR * HN * KA * NB \

.

Commuta NL se bit (KA) = 1.

OR * HN \ * NK * NL \

.

Scrive il bit di parità.

In lettura cartolina OS * LS * AP \ memorizza i bit letti.

In radice quadrata abilita il 2° ciclo degli stati SF, SG, SH, SK.

WR (ZK * SK * NM \) commuta NL ogni SK se NM negato.

Sommatore

document: P101- Fogli logici. Foglio 5.

Con sommatore si intende un complesso circuitale utilizzato per operazioni di conta,

somma algebrica o confronto.

Il sommatore è composto da:

• Sommatore binario parallelismo 1 bit.

• NL - Rete logica di segno discorde in A e M. Segno discorde NL = 1.

• NK - Segno registro A, accumulatore. Segno meno NK = 1.

• VB - Rete logica di decisione somma algebrica. Ciclo di somma VB = 1.

• XM – Rete logica combinatoria. Bit 1 di somma, confronto o conta.

• XS - Rete logica combinatoria. Bit 2 di somma o confronto.

• ND - Riporto di bit e digit.

• NE – Riporto bit o digit precedente e\o incremento contatore.

• NM – Risultato confronto A > M.

• VS – Formattazione output sommatore.

A completamento è incluso il registro di uso multiplo(KA–KH), utilizzato dal sommatore

per:

• Far scorrere il registro di un Crt rispetto gli altri.

• Inserire a posteriore un bit di servizio, per la eventuale correzione.

• Conta posizioni Crt in LDR .

I dati oggetto di calcolo sono posti in M e A, registri interi.

Il risultato del calcolo, a fine calcolo, si trova formattato in A, stato SL.

Il registro R è utilizzato, durante il calcolo, come registro di servizio.

A fine calcolo contiene dati utili, il cui significato diverso, dipende dall’istruzione.

Le funzioni che utilizzano il sommatore sono:

55•

•

•

•

Scrittura dei bit di controllo temporizzazione della LDR.

Impostazione della numero di cifre decimali da rotella.

Esecuzione delle istruzioni di calcolo.

Conta denti ruota in stampa.

Le operazioni elementari sono:

• Conteggio Crt.

• Confronto registri.

• Somma di bit.

• Somma di digit decimali.

PA, PM, TP e TM

PA, PM e TP, delimitano la parte di registro contenente dati validi. Il criterio di scelta è

presenza di bit TB = 1 contigui.

Questa funzione risolve il problema di registri che durante l’elaborazione possono far

scorrere, shiftare, la loro posizione in linea di ritardo.

PA, PM sono correlati al registro A e M.

TP svolge la stessa funzione logica per il registro selezionato tra quelli in LT (A, M, R, B,

C, D, E, F) .

PA e PM in or originano PO, segnale che spesso determina il cambio stato.

Con i registri deposito splittati che possono contenere due dati numerici, la scelta del dato

indicato dall’istruzione è fatta tramite il flip flop TM.

Il set di TM dipende dal bi HD dell’istruzione:

• HD = 0

Set tramite TA in B sul 24° Crt.

• HD = 1

Set tramite TA in C sul 12° Crt.

TM permane per 1 solo Crt, il suo reset avviene il TA seguente

L a caduta di TM setta TP all’inizio del registro, 1° o 13° Crt.

TP, è set per la parte di registro individuata da HD e con Crt contigui aventi TB=1.

HP

Il flip flop HP indica che è in esecuzione un programma.

Esso è settato da XI (CS * LR * TA * SA \ * NH \ ), segnale che inizia la fase di fetch da

registro programma dell’istruzione da eseguire.

Il reset di HP avviene con l’estrazione, da registro di programma, dell’istruzione S

Istruzione che a seconda della logica del programma, pone lo stesso in attesa

dell’intervento dell’operatore o ne segnala la fine.

===Decodifica codice istruzione===.

P101- Fogli logici. Foglio 3.

Il registro H contiene il codice dell’istruzione in esecuzione, specificamente in:

HA – HC

Codice del registro.

HD

Registro intero (0), splittato (1).

HE – HH

Codice operativo.

Dai codici derivano specifici decodificati hardware di indirizzo e codice operativo.

Decodifica codice indirizzo registro - DX

P101- Fogli logici. Foglio 3.

I decodificati di registro sono 8, la lettera dopo la D è quella del registro.

In ordine binario:

Decodificato

DM

DC

DR

DD

DA

DB

DF

DE

Hex

0

1

2

3

4

5

6

7

HA

0

1

0

1

0

1

0

1

HB

0

0

1

1

0

0

1

1

HC

0

0

0

0

1

1

1

1

Per i soli registri deposito B, C, D, E, F , ponendo il bit HD = 1, si seleziona il registro

indicato in HA – HC, di soli 12 Crt con inizio dal 13° Crt.

I registri aventi HD = 1 sono detti splittati e nei fogli di programmazione sono indicati con

lettere minuscole.

I registri solo programma G ed I, essendo acceduti in sequenza non necessitano di

specifico indirizzo. Dovendo comunque essere distinti per essere utilizzati, si usano i

decodificati DM e DA, rispettivamente per G ed I.

La condivisione dei due decodificati è resa possibile dalle funzioni, tra loro esclusive, che

utilizzano i due tipi di registri.

Da tastiera HD è posto a 1

istruzione.

dal tasto Split (\), inserito tra il tasto indirizzo e quello

Decodifica codice operativo - ZX

P101- Fogli logici. Foglio 3.

I decodificati delle istruzioni sono utilizzati per identificare sia un solo codice operativo

che un insieme di codici operativi.

Un solo codice operativo può attivare più decodificati.

Ad esempio la radice quadrata , codice operativo B Hex, attiva i decodificati:

ZA

ZC

ZK

Calcolo

Moltiplicazione, Divisione, Radice quadrata.

Radice quadrata.

In ordine binario:

Decodificato

ZN

ZG

ZH

ZB

ZE

ZF

ZL

ZK

ZM

Istruzione

S

↓, ↕

↑

+, -

X

<>, *

√

V, W,X,Y

Hex

0

1, 3

2

4, 5

6

7

8, 9

B

C- F

HE

0

X

0

X

0

1

X

1

X

HF

0

0

1

0

1

1

0

1

X

HG

0

0

0

1

1

1

0

0

1

HH

0

0

0

0

0

0

1

1

1

Il codice operativo A Hex non è utilizzato.

ZA si attiva per tutti i codici operativi di calcolo più VX, costante da programma.

ZC si attiva per moltiplicazione, divisione , radice quadrata.

ZO viene attivato per i codici di trasferimento registri, stampa, e ZA * SB * NH \ .

Schema a blocchi

image

Parte 3. Hardware comune

Lettura o scrittura in Linea di Ritardo

L’operazione di lettura o scrittura in LDR, in caso di interazione con tastiera, cartolina e

stampa, utilizza una struttura hardware unica indipendentemente dal contenuto

semantico del dato scambiato (Esempio numero o istruzione).

I segnali di

• AK

• WX

• HN

• VZ

richiesta sono:

Crt da tastiera.

Crt da stampare.

Crt in input o output verso cartolina.

Avvio stampa per risultato calcolo manuale X : e radice.

La struttura si compone di:

• WZ

Or delle richieste.

• PS

Flip flop si sincronizzazione con temporizzazione di Crt.

• NG

Flip flop di abilitazione richiesta.

• NA – NB Coppia di Flip flop di attuazione della richiesta.

Il flip flop PS, sincronizza l’insieme delle richieste asincrone di scambio Crt, rispetto la

temporizzazione di sistema, usando il 1° fronte di TD per il set e di TH per il reset.

Il flip flop NA:

Set con XE:

• TA in R

Tastiera e Cartolina.

• TA in A

Stampa.

Blocca la scrittura del TA in R o A se occorre spostarlo sul Crt seguente.

Abilita la scrittura del Crt nel registro K.

Il reset di NA avviene il TA seguente e con esso si ha il set di NB .

Il flip flop NB:

Scrive il TA in R o A, se occorre sul carattere seguente.

Setta NG impedendo che il ciclo seguente si abbia un nuovo ciclo NA – NB .

Un nuovo ciclo si riavrà solo a seguito di un nuova richiesta di scambio Crt con LDR con

NG reset.

Il diagramma mostra il caso di stampa della cifra 6 in M.

Diagramma Ciclo NA - NB

Il TA di A è sul 1° Crt, esso genera XE che setta NA.

NA blocca la riscrittura del TA in RA.

60La cifra 6 in LM, complementato 9, viene caricata in K per il conteggio successivo coi

denti della ruota fonica.

Il reset di NA setta il flip flop NB .

Il flip flop NB:

Abilita la scrittura del TA in RA ritardato di 1 Crt.

Setta il flip flop NG che bloccando XE impedisce cicli supplementari di NA – NB .

Introduzione dati

La via primaria di introduzione dati è la tastiera.

L’introduzione di dati è permessa solo in SA, stato in cui la tastiera è sbloccata.

Da tastiera si introducono sia i dati per l’utilizzo della P101 come esecutore di singole

istruzioni, che i codici delle istruzioni di un programma da eseguirsi successivamente.

La distinzione tra le diverse modalità è descritta a pagina 36 di questo documento

(Pulsanti Introduzione e Stampa Programma).

Se i dati numerici, sono seguiti da istruzioni di salto o start, si avvia il programma

precedentemente inserito.

Se l’istruzione introdotta è diversa da salto o start, si ha l’esecuzione immediata

dell’istruzione con :

• Stampa dati e istruzione.

• Esecuzione immediata della istruzione.

• Ritorno in SA in attesa nuovo intervento operatore.

Anche con programma introdotto da cartolina, il suo avvio avviene da tastiera con

l’inserimento del codice dell’istruzione tra S, V, W, Y, Z.

I cicli meccanici di tastiera, attivano con i μSwitch di codice, il μSwitch AK avente funzione

di strobe.

Fanno eccezione il 1° ciclo di reset ed i tasti virgola e segno meno che non attivano AK.

I micro AE ed AF codificano con:

• 00 Dato numerico.

• 11 Indirizzo di registro.

• 01 Codice di istruzione.

I micro AA – AD, rappresentano il codice di dato numerico, indirizzo o istruzione. In ogni

caso detto codice viene memorizzato nel registro K (KA – KD).

In Appendice A. Codici da tastiera, si trova il dettaglio dei codici attribuiti ai tasti.

La sequenza degli eventi di gestione è la stessa per ogni tipo di tasto, con:

AK

Strobe del codice.

PS

Strobe sincronizzato alla temporizzazione di Crt.

NG

Assicura 1 solo codice a battuta tasto.

NA

Attivo sul Crt del TA in R.

NB

Attivo sul Crt seguente il TA in R.

Dato numerico

I dati numerici, contraddistinti da AE e AF entrambi a 0, sono memorizzati nel registro

M.

La cifra (digit) è inserita nel Crt seguente quello corrispondente al TA di R.

L’inserimento della 1° cifra numerica con WE ( SA * PS * NM \ * AF \ * CT \), azzera di M

cancellando il numero precedente.

La posizione del puntatore TA in R è indeterminata. Il TA in R, è utilizzato pure come

puntatore dell’istruzione da eseguire, quindi la sua posizione dipende dalla logica di un

eventuale programma.

Durante la fase di introduzione del dato il TA in R, rimane fisso, i Crt inseriti

precedentemente lasciano il posto al nuovo essendo ritardati in blocco da un giro con K

inserito, XD ( CG * LM * ND * WM \ * YD \). Ciò è necessario se si è interrotta

l’esecuzione del programma per introdurre un dato e riavviare il programma dal punto di

interruzione.

La battuta dei tasti segno meno (AM), virgola (AV), clear (AN), viene memorizzata

rispettivamente in NE, NF, NC.

A seguito del tasto di segno meno (AM), SA * NE * PM * TC * CT \, inserisce il bit TC, su

tutti i Crt di M con PM attivo.

Il tasto di segno meno esegue la sua funzione anche se è battuto prima del tasto

istruzione .

Il codice è completato da XG (SA * NB * UH4 * AF \ * CT \), che inserisce tramite UH4

(WM + TB), i bit di servizio TB e TD sull’ultima cifra introdotta.

La virgola rappresentata dal bit TD in WM ( SA * TD * NF \), è bloccata se NF = 1.

WM stesso blocca il TD in XD (CG * LM * ND * WM \ * YD \), via di richiusura tramite K di

M.

Si ottiene che la virgola (TD), accompagna sempre l’ultima cifra battuta sino alla battuta

del tasto di virgola, che attivando NF ne fissa la posizione sulla cifra delle unità.

Si nota che in ogni caso, un numero senza decimali la cifra delle unità ha il TD =1.

Il diagramma presenta l’introduzione di 234,56 e↑, l’operatore dopo aver introdotto 234 erra

battendo il meno (AM), corregge con Clear (AN), termina introducendo correttamente 234,56 e↑.

Diagramma Introduzione dato con tasto Clear.

Il diagramma mostra l’inserzione dell’ultima cifra decimale 6, nel Crt individuato da NB

con il shift relativo delle cifre 234,5 , introdotte precedentemente.

Diagramma Inserzione cifra.

62Il tasto Clear (AN) setta NC e il gate VW (SA * AN * AP \), resetta NE ed NM.

VH (SA * AK * NM \), tasto con NM reset, resetta NF.

Un successivo tasto numerico o istruzione, attivando XW resetta NC.

Diagramma Tasto Clear.

Indirizzo

Un tasto indirizzo attiva entrambi AE ed AF.

La sequenza di eventi di gestione del tasto è uguale a quella dei tasti numerici con la

differenza che AF = 1, indirizzo o istruzione, blocca la scrittura del codice in M.